**Embedded Systems**

## Embedded Software Design and Programming of Multiprocessor System-on-Chip

Simulink and System C Case Studies

Katalin Popovici · Frédéric Rousseau Ahmed A. Jerraya · Marilyn Wolf

## **Embedded Systems**

#### **Series Editors**

Nikil D. Dutt, Department of Computer Science, Zot Code 3435, Donald Bren School of Information and Computer Sciences, University of California, Irvine, CA 92697-3435, USA

Peter Marwedel, TU Dortmund, Informatik 12, Otto-Hahn-Str. 16, 44227 Dortmund, Germany

Grant Martin, Tensilica Inc., 3255-6 Scott Blvd., Santa Clara, CA 95054, USA

Katalin Popovici · Frédéric Rousseau · Ahmed A. Jerraya · Marilyn Wolf

# Embedded Software Design and Programming of Multiprocessor System-on-Chip

Simulink and SystemC Case Studies

Katalin Popovici MathWorks, Inc. 3 Apple Hill Dr. Natick MA 01760 USA katalin.popovici@mathworks.com

Ahmed A. Jerraya Laboratoire TIMA 46 av. Felix Viallet 38031 Grenoble CX France ahmed.jerraya@cea.fr Frédéric Rousseau Laboratoire TIMA 46 av. Felix Viallet 38031 Grenoble CX France frederic.rousseau@imag.fr

Marilyn Wolf Georgia Institute of Technology Electrical & Computer Engineering Dept. 777 Atlantic Drive NW. Atlanta GA 30332-0250 Mail Stop 0250 USA marilyn.wolf@ece.gatech.edu

ISBN 978-1-4419-5566-1 e-ISBN 978-1-4419-5567-8 DOI 10.1007/978-1-4419-5567-8 Springer New York Dordrecht Heidelberg London

Library of Congress Control Number: 2009943586

#### © Springer Science+Business Media, LLC 2010

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

## Acknowledgments

The authors would like to thank for the very useful comments of the book reviewers, which contributed a lot to improve the book, and the remarks and suggestions of all the persons for reading parts of the manuscript. We would especially like to thank Grant Martin (Tensilica Inc., USA), Tiberiu Seceleanu (ABB Corporate Research, Sweden), Soo Kwan Eo (Samsung Electronics'SoC R&D Center, Korea), Frank Schirrmeister (Synopsys Inc., USA), Lovic Gauthier (Fukuoka Laboratory for Emerging & Enabling Technology of SoC, Japan), Jason Agron (University of Arkansas, USA), Wido Kruijtzer (NXP Semiconductors, Eindhoven, Netherlands), Felice Balarin (Cadence, San Jose CA, USA), Pierre Paulin (STMicroelectronics, Ottawa, Canada), Brian Bailey (Brian Bailey Consulting, Oregon, USA).

Finally we would like to thank Mr. Charles Glaser from Springer for his wonderful cooperation in publishing this book.

## **Contents**

| I | Emi  | beaaea | Systems Design: Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|---|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | and  | Softwa | re Interaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1  |

|   | 1.1  | Introd | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1  |

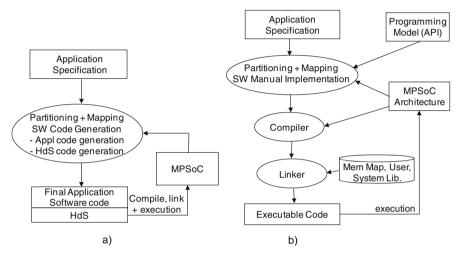

|   | 1.2  | From   | Simple Compiler to Software Design for MPSoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7  |

|   | 1.3  | MPSo   | C Programming Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3  |

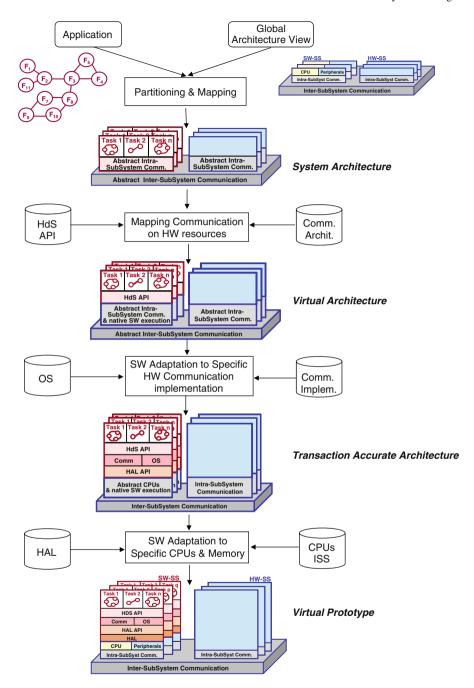

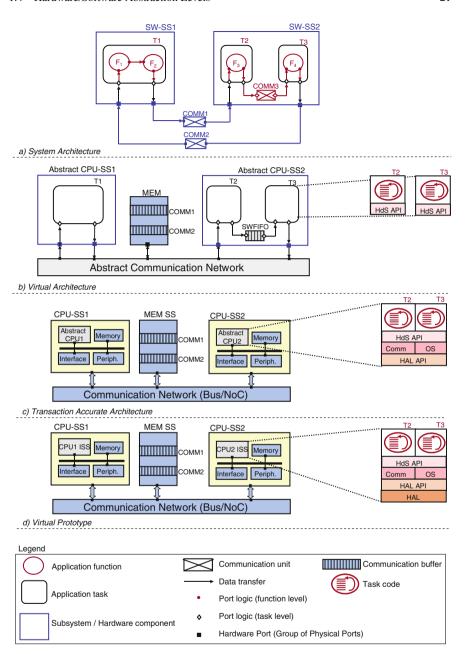

|   | 1.4  | Hardw  | vare/Software Abstraction Levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6  |

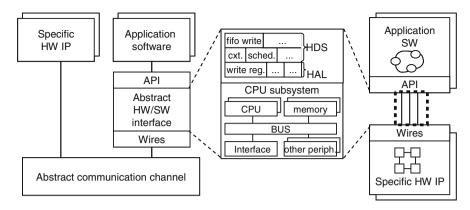

|   |      | 1.4.1  | The Concept of Hardware/Software Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8  |

|   |      | 1.4.2  | Software Execution Models with Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|   |      |        | Hardware/Software Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20 |

|   | 1.5  | The C  | oncept of Mixed Architecture/Application Model 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 24 |

|   |      | 1.5.1  | Definition of the Mixed Architecture/Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|   |      |        | Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24 |

|   |      | 1.5.2  | Execution Model for Mixed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|   |      |        | Architecture/Application Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25 |

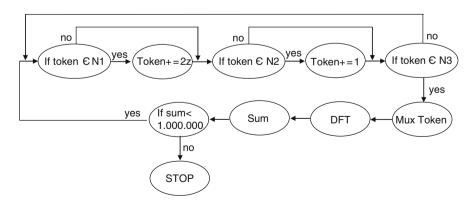

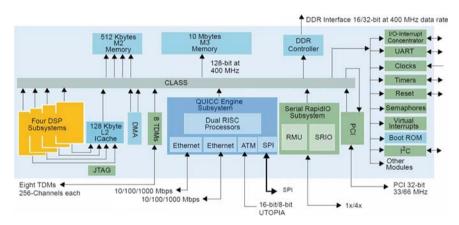

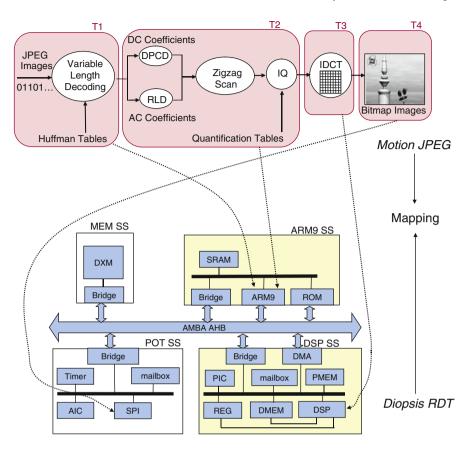

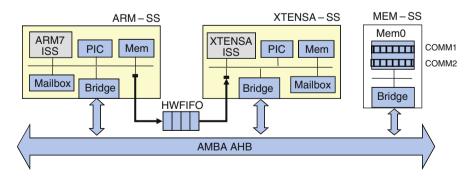

|   | 1.6  | Examp  | oles of Heterogeneous MPSoC Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31 |

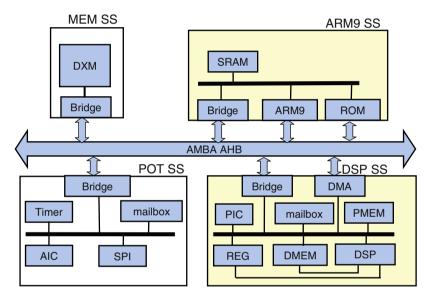

|   |      | 1.6.1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31 |

|   |      | 1.6.2  | The state of the s | 3  |

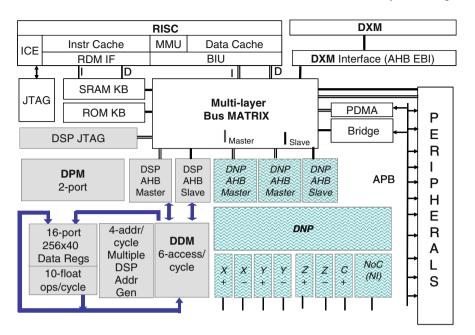

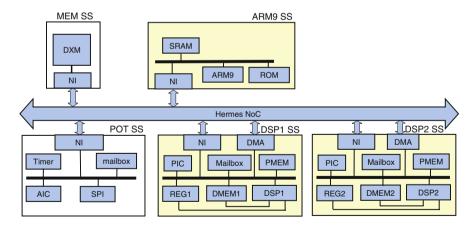

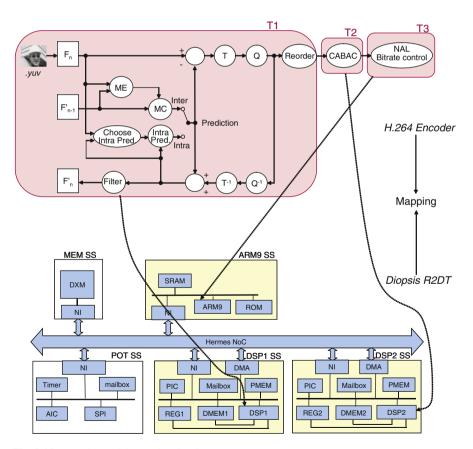

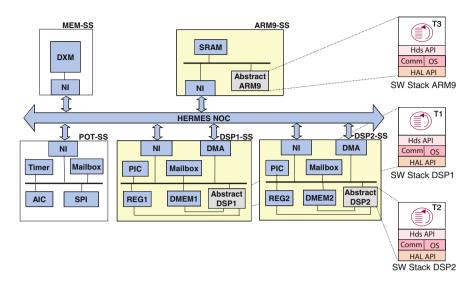

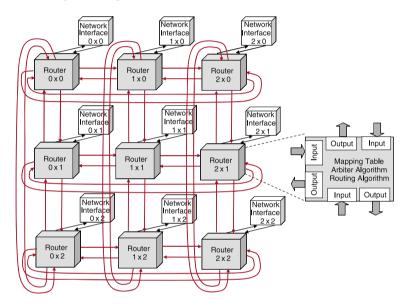

|   |      | 1.6.3  | Diopsis R2DT with NoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6  |

|   | 1.7  | Examp  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9  |

|   |      | 1.7.1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10 |

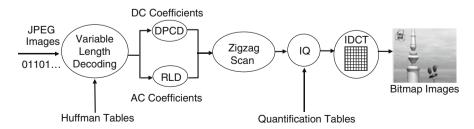

|   |      | 1.7.2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -1 |

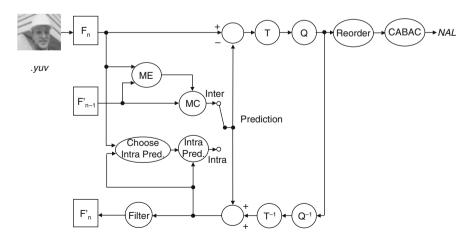

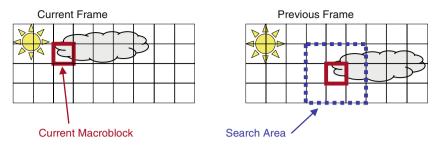

|   |      | 1.7.3  | H.264 Encoder Functional Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13 |

|   | 1.8  | Concl  | asions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17 |

| 2 | Basi | ics    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19 |

|   | 2.1  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19 |

|   | 2.2  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 51 |

|   |      | 2.2.1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 54 |

|   |      | 2.2.2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5  |

|   |      | 2.2.3  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6  |

|   |      | 2.2.4  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8  |

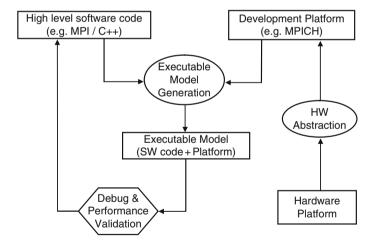

|   | 2.3  | Softwa |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5  |

|   |      | 2.3.1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5  |

viii Contents

|   |      | 2.3.2    | Software Stack Organization                     | 66  |

|---|------|----------|-------------------------------------------------|-----|

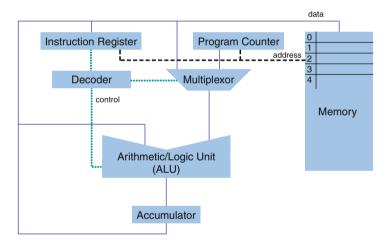

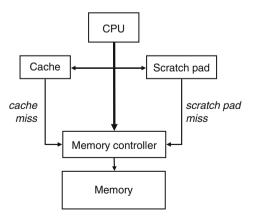

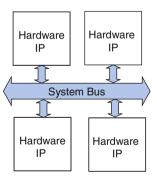

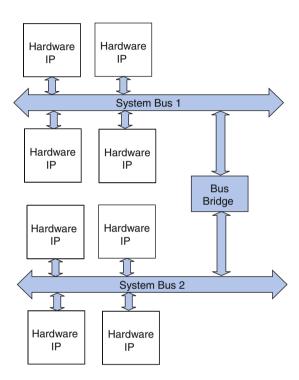

|   | 2.4  | Hardw    | vare Components                                 | 69  |

|   |      | 2.4.1    | Computing Unit                                  | 69  |

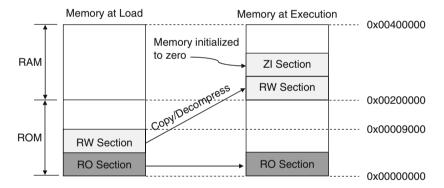

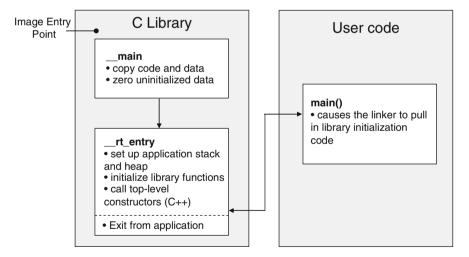

|   |      | 2.4.2    | Memory                                          | 77  |

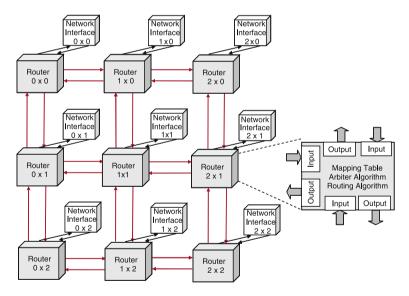

|   |      | 2.4.3    | Interconnect                                    | 80  |

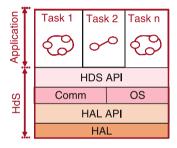

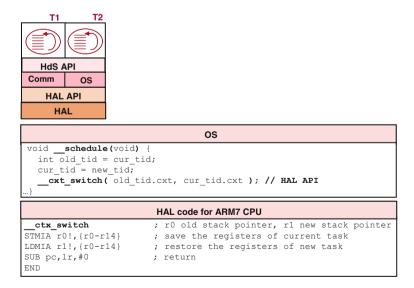

|   | 2.5  | Softwa   | are Layers                                      | 84  |

|   |      | 2.5.1    | Hardware Abstraction Layer                      | 86  |

|   |      | 2.5.2    | Operating System                                | 87  |

|   |      | 2.5.3    | Communication and Middleware                    | 92  |

|   |      | 2.5.4    | Legacy Software and Programming Models          | 92  |

|   | 2.6  | Conclu   | usions                                          | 92  |

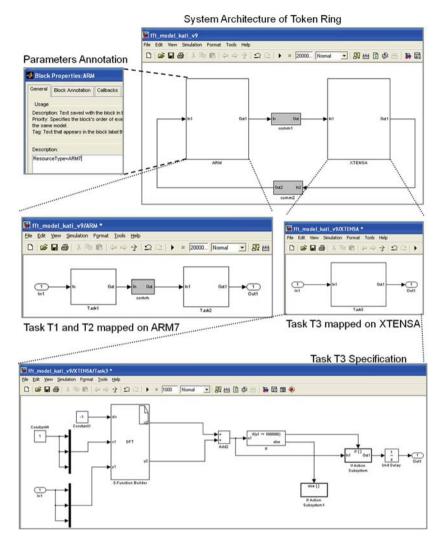

| 3 | Syst | em Arc   | chitecture Design                               | 93  |

|   | 3.1  |          | uction                                          | 93  |

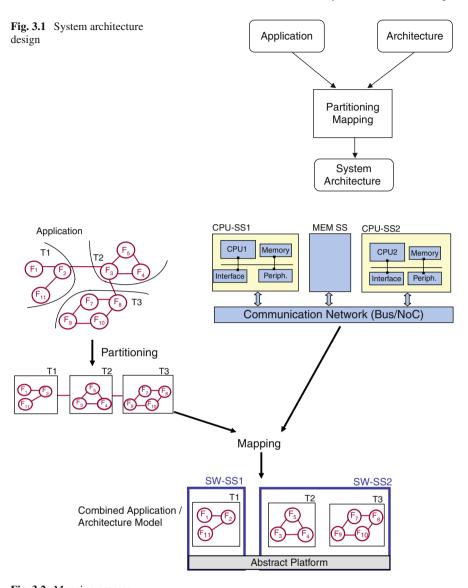

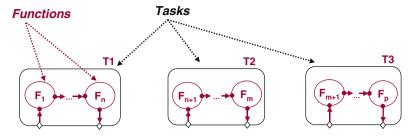

|   |      | 3.1.1    | Mapping Application on Architecture             | 93  |

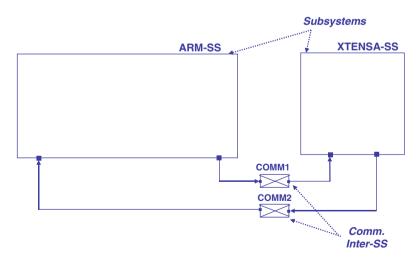

|   |      | 3.1.2    | Definition of the System Architecture           | 97  |

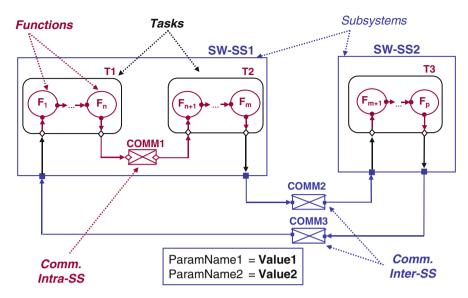

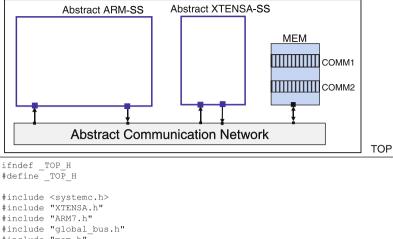

|   |      | 3.1.3    | Global Organization of the System Architecture  | 98  |

|   | 3.2  | Basic    | Components of the System Architecture Model     | 101 |

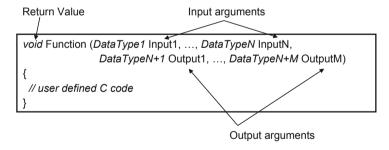

|   |      | 3.2.1    | Functions                                       | 101 |

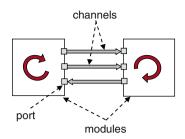

|   |      | 3.2.2    | Communication                                   | 102 |

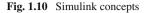

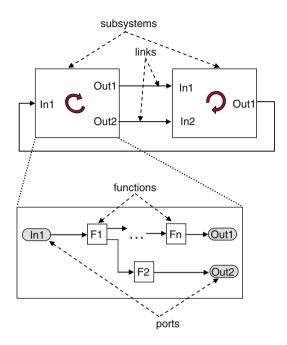

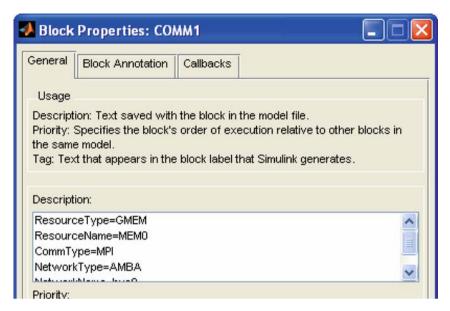

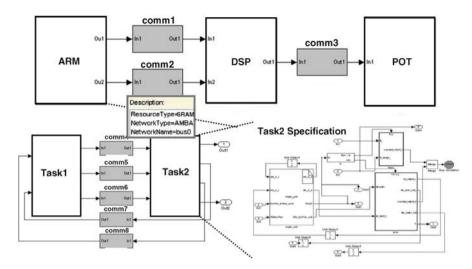

|   | 3.3  | Model    | ling System Architecture in Simulink            | 102 |

|   |      | 3.3.1    | Writing Style, Design Rules, and Constraints    |     |

|   |      |          | in Simulink                                     | 102 |

|   |      | 3.3.2    | Software at System Architecture Level           | 104 |

|   |      | 3.3.3    | Hardware at System Architecture Level           | 105 |

|   |      | 3.3.4    | Hardware–Software Interface at System           |     |

|   |      |          | Architecture Level                              | 106 |

|   | 3.4  | Execu    | tion Model of the System Architecture           | 106 |

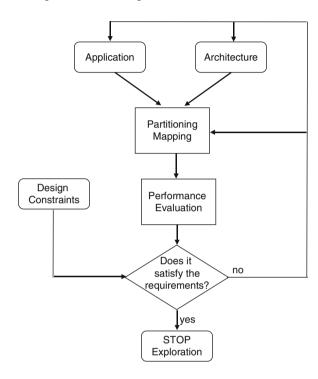

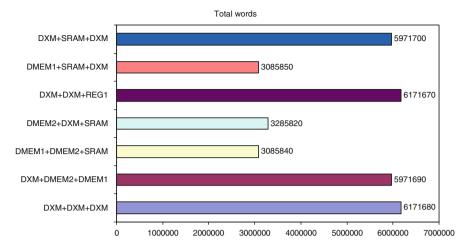

|   | 3.5  | Design   | n Space Exploration of System Architecture      | 106 |

|   |      | 3.5.1    | Goal of Performance Evaluation                  | 106 |

|   |      | 3.5.2    | Architecture/Application Parameters             | 107 |

|   |      | 3.5.3    | Performance Measurements                        | 109 |

|   |      | 3.5.4    | Design Space Exploration                        | 110 |

|   | 3.6  | Applic   | cation Examples at the System Architecture      |     |

|   |      | Level    |                                                 | 111 |

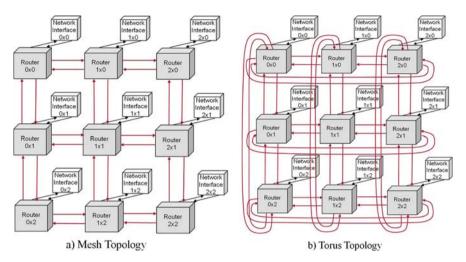

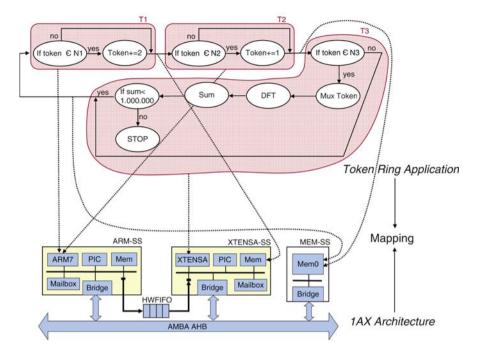

|   |      | 3.6.1    | Motion JPEG Application on Diopsis RDT          | 111 |

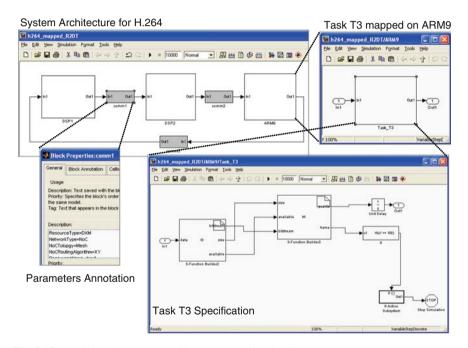

|   |      | 3.6.2    | H.264 Application on Diopsis R2DT               | 114 |

|   | 3.7  | State of | of the Art and Research Perspectives            | 118 |

|   |      | 3.7.1    | State of the Art                                | 118 |

|   |      | 3.7.2    | Research Perspectives                           | 119 |

|   | 3.8  | Conclu   | usions                                          | 120 |

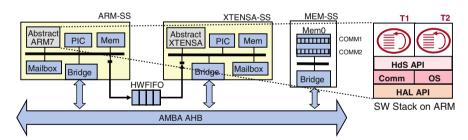

| 4 | Virt | ual Arc  | chitecture Design                               | 123 |

|   | 4.1  | Introd   | uction                                          | 123 |

|   |      | 4.1.1    | Definition of the Virtual Architecture          | 123 |

|   |      | 4.1.2    | Global Organization of the Virtual Architecture | 124 |

Contents ix

|   | 4.2  | Basic   | Components of the Virtual Architecture Model         | 125 |

|---|------|---------|------------------------------------------------------|-----|

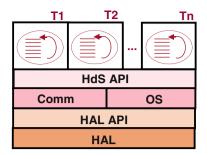

|   |      | 4.2.1   | Software Components                                  | 126 |

|   |      | 4.2.2   | Hardware Components                                  | 126 |

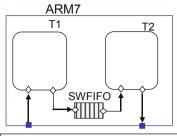

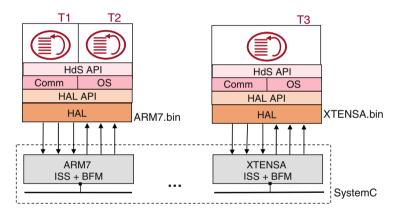

|   | 4.3  | Mode    | ling Virtual Architecture in SystemC                 | 127 |

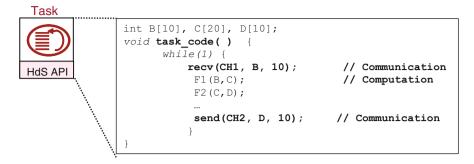

|   |      | 4.3.1   | Software at Virtual Architecture Level               | 127 |

|   |      | 4.3.2   | Hardware at Virtual Architecture Level               | 130 |

|   |      | 4.3.3   | Hardware-Software Interface at Virtual               |     |

|   |      |         | Architecture Level                                   | 134 |

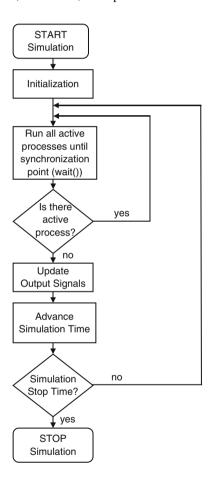

|   | 4.4  | Execu   | ation Model of the Virtual Architecture              | 134 |

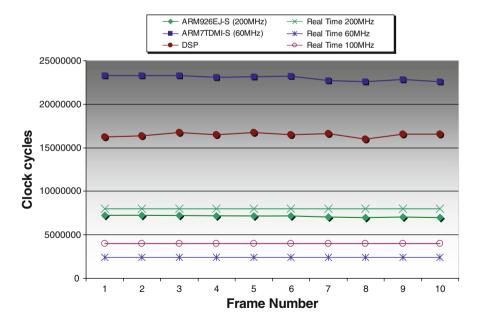

|   | 4.5  | Desig   | n Space Exploration of Virtual Architecture          | 136 |

|   |      | 4.5.1   | Goal of Performance Evaluation                       | 136 |

|   |      | 4.5.2   | Architecture/Application Parameters                  | 136 |

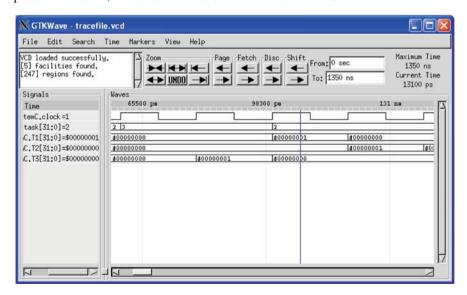

|   |      | 4.5.3   | Performance Measurements                             | 137 |

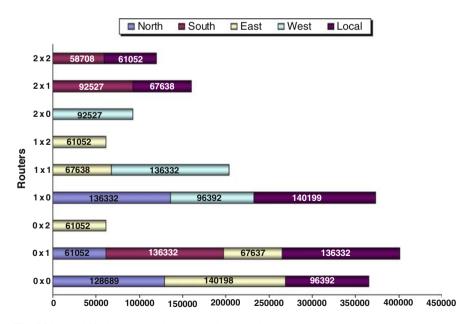

|   |      | 4.5.4   | Design Space Exploration                             | 139 |

|   | 4.6  | Applie  | cation Examples at the Virtual Architecture Level    | 139 |

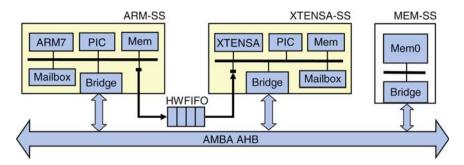

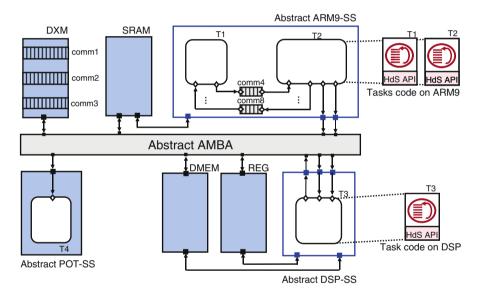

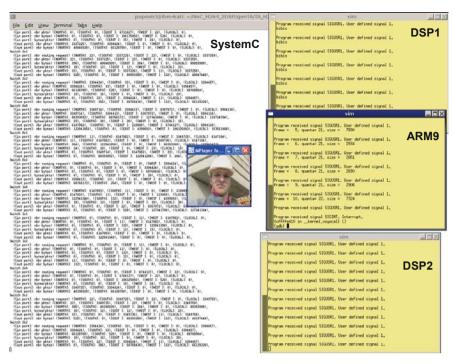

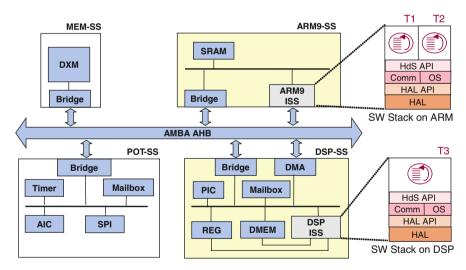

|   |      | 4.6.1   | Motion JPEG Application on Diopsis RDT               | 139 |

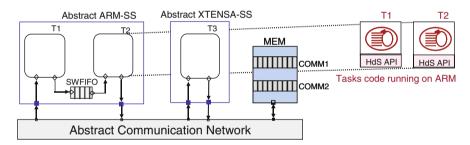

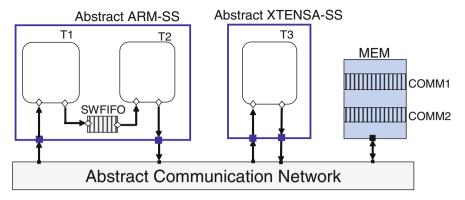

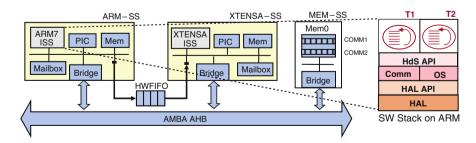

|   |      | 4.6.2   | H.264 Application on Diopsis R2DT                    | 143 |

|   | 4.7  | State   | of the Art and Research Perspectives                 | 147 |

|   |      | 4.7.1   | State of the Art                                     | 147 |

|   |      | 4.7.2   | Research Perspectives                                | 148 |

|   | 4.8  | Concl   | usions                                               | 149 |

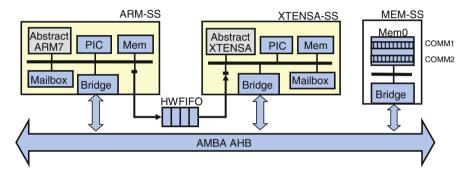

| 5 | Trai | nsactio | n-Accurate Architecture Design                       | 151 |

| • | 5.1  |         | luction                                              | 151 |

|   | 0.1  | 5.1.1   | Definition of the Transaction-Accurate Architecture  | 152 |

|   |      | 5.1.2   | Global Organization of the Transaction-Accurate      | 102 |

|   |      | 0.1.2   | Architecture                                         | 152 |

|   | 5.2  | Basic   | Components of the Transaction-Accurate               |     |

|   |      |         | tecture Model                                        | 154 |

|   |      | 5.2.1   | Software Components                                  | 155 |

|   |      | 5.2.2   | Hardware Components                                  | 155 |

|   | 5.3  |         | ling Transaction-Accurate Architecture in SystemC    | 156 |

|   | 0.0  | 5.3.1   | Software at Transaction-Accurate Architecture        | 100 |

|   |      | 0.0.1   | Level                                                | 156 |

|   |      | 5.3.2   | Hardware at Transaction-Accurate Architecture Level  | 161 |

|   |      | 5.3.3   | Hardware–Software Interface at Transaction-          | 101 |

|   |      | 0.0.0   | Accurate Architecture Level                          | 164 |

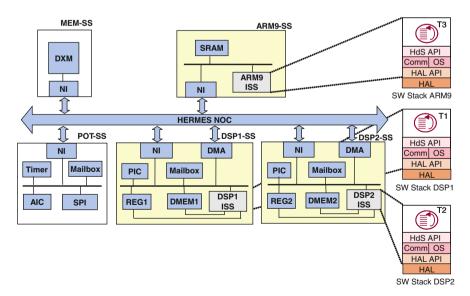

|   | 5.4  | Execu   | ition Model of the Transaction-Accurate Architecture | 164 |

|   | 5.5  |         | n Space Exploration of Transaction-Accurate          | 101 |

|   | 5.5  |         | tecture                                              | 166 |

|   |      | 5.5.1   | Goal of Performance Evaluation                       | 166 |

|   |      | 5.5.2   | Architecture/Application Parameters                  | 167 |

|   |      | 5.5.3   | Performance Measurements                             | 167 |

|   |      | 5.5.4   | Design Space Exploration                             | 168 |

|   |      |         |                                                      |     |

x Contents

|     | 5.6   | Application Examples at the Transaction-Accurate       | 69 |

|-----|-------|--------------------------------------------------------|----|

|     |       |                                                        | 69 |

|     |       | **                                                     | 72 |

|     | 5.7   |                                                        | 80 |

|     | 3.7   |                                                        | 80 |

|     |       |                                                        | 81 |

|     | 5.8   | •                                                      | 82 |

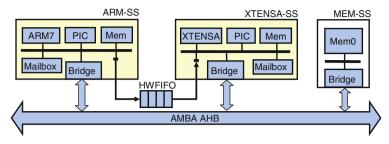

| 6   |       |                                                        | 83 |

| U   | 6.1   |                                                        | 83 |

|     | 0.1   |                                                        | 83 |

|     |       |                                                        | 85 |

|     | 6.2   |                                                        | 85 |

|     | 0.2   |                                                        | 85 |

|     |       |                                                        | 86 |

|     | 6.3   | 1                                                      | 87 |

|     | 0.0   |                                                        | 87 |

|     |       | * <del>*</del>                                         | 94 |

|     |       | 6.3.3 Hardware–Software Interface at Virtual Prototype |    |

|     |       | • •                                                    | 94 |

|     | 6.4   |                                                        | 95 |

|     | 6.5   | Design Space Exploration of Virtual Prototype          | 96 |

|     |       | 6.5.1 Goal of Performance Evaluation                   | 96 |

|     |       | 6.5.2 Architecture/Application Parameters              | 97 |